# 縦型 GaN トレンチ MOSFET 開発とインバータ動作実証

西井潤弥<sup>\*1</sup>, 長谷川一也<sup>\*1</sup>, 田中成明<sup>\*1</sup>, 丹羽隆樹<sup>\*1</sup>

## Progress in Development of a Vertical GaN Trench MOSFET, and an Inverter Demonstration

Junya Nishii<sup>\*1</sup>, Kazuya Hasegawa<sup>\*1</sup>, Nariaki Tanaka<sup>\*1</sup>, Takaki Niwa<sup>\*1</sup>

### 要旨

縦型 GaN トレンチ MOSFET を試作し、ハーフブリッジモジュールと三相インバータモジュールでの動作実証を行った。インバータモジュールでの出力は目標の 10 kW に到達した。

### Abstract

Vertical GaN trench MOSFETs were fabricated and their operation was verified in a half-bridge module and a three-phase inverter module. The inverter module output reached the target of 10 kW.

## 1. はじめに

本稿は、豊田合成が令和4年から参画している<sup>1)</sup>、環境省による『超低抵抗GaN ウェハを用いた高効率インバータの開発・検証事業』(以下『環境省pj』と略する)での開発進捗、特にデバイス開発からインバータモジュールでの動作検証について報告する<sup>2)</sup>。

### 1-1. 背景と周辺技術

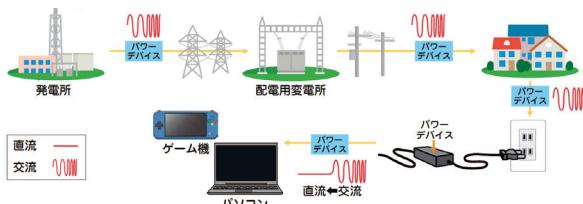

近年、自動車の電動化やAI、仮想現実技術などの発達により、電子部品やデータサーバーなどの需要が旺盛である。これに従い、電子部品群が消費する電力量も増大の一途である。電力は、発電所やバッテリーなどの供給源から様々な経路で最終消費地まで運ばれるが、その過程で電圧の変圧、交流から直流、あるいは直流から交流への変換など様々な『変換』を経る(図-1)。この電力の変換を担う電気回路技術をパワーエレクトロニクスと呼び、その根幹部品が半導体を用いたパワーデバイス(トランジスタ、ダイオード)である。

図-1 送電経路の模式図とパワーデバイス

各種の電力変換の際には、一部の電力エネルギーが熱エネルギーとして放出されてしまう。これを電力損失という。発電所から最終消費地に届くまでの電力損失は発電時の電力に対して 26 % に達するとの試算もあり<sup>3)</sup>、電力需要の増加の中、電力損失を抑える省エネ技術が必要不可欠である。電力損失を抑え効率良く電力を変換するためには、炭化ケイ素や窒化ガリウム(GaN)などのワイドバンドギャップ半導体と呼ばれる新しい半導体の優れた物性を活用することが有効である。

豊田合成では、青色発光ダイオードをベースにしたGaN関連の技術を活用して、GaNの種結晶開発とパワーデバイス開発に取り組んでいる。種結晶開発では、大阪大学との共同開発により6インチサイズの大口径結晶の育成に成功し、GaNの単結晶ウェハの大口径化、高品質化技術に貢献している<sup>4)</sup>。またこれを受けて、GaNウェハ上のGaNデバイスの研究開発が活発化してきている。GaNウェハ上の縦型GaNパワーデバイスは次世代の高出力・高速動作を実現するものとして注目されており様々なデバイス構造が提案されている<sup>5)~8)</sup>。特に出力電流を制御するゲート電極周辺の設計が、金属/絶縁体/半導体(MOS: Metal Oxide Semiconductor)構造の電界効果トランジスタ(FET: Field Effect Transistor)は電圧駆動でドライブ回路がシンプルであり、比較的高いしきい値電圧により動作不良を回避しやすいため、高い信頼性、長寿命が求められるパワーデバイス用途には不可欠なデバイスと考えられて

<sup>\*1</sup> 新価値第1技術部 GaN パワーデバイス技術室

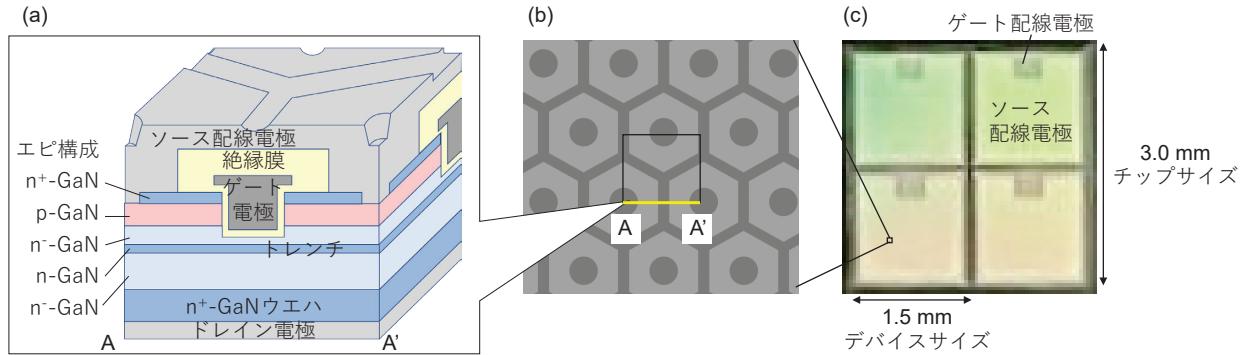

図-2 縦型GaNトレンチMOSFET

(a) トランジスタセルの鳥瞰模式図、(b) セル上面イメージ (c) 試作したチップの写真

いる<sup>9)~12)</sup>。図-2は、豊田合成が開発している縦型GaNトレンチMOSFET（以下、「縦GaN MOSFET」と略称する）の模式図、写真類である。これまでに、単一セルでの原理実証を経て3mm×3mmサイズのマルチセルデバイスでの動作報告を行ってきた<sup>11), 12)</sup>。しかしながら、性能のバラツキ、再現性などの課題があり、以降、信頼性、プロセス再現性の改善に取り組んできた。その間、冒頭に述べたようにGaNウエハの高品質化が進み、これによりデバイスの試作歩留まりが向上し、数mmサイズのデバイスも再現よく作製することができるようになってきたことを受け、環境省pjでのインバータ搭載、動作検証に挑戦することになった。

## 2. デバイス開発

### 2-1. デバイス作製

市販されているn<sup>+</sup>-GaNウエハ上に、図-2 (a)に示すエピ構成を有機金属気相成長法にて結晶成長し、リセス、トレンチをGaN上にドライエッチングで形成する。続いて、ソース電極、ゲート絶縁膜、ゲート電極などを成膜する。作製したデバイスは上面から見ると六角形のセル状になっており、この“セル”を数万～十数万個、ハニカム状に並べて一つのデバイスを形成する（図-2 (b)）。各セルの電極は、配線電極で接続されている。最後に、GaNウエハの裏面にドレイン電極を形成する。プロセスの詳細は参考文献<sup>11), 12)</sup>を参照されたい。

このようにして、一辺が1.5mmの縦GaNデバイスを作製する。チップサイズは、実装工程、モジュール設計の都合上、一辺を3mmとしたので、1チップ上に4つのデバイスが形成されることになる（図-2 (c)）。各デバイスの上辺の中央に配置されているのがゲートの配線電極、それ以外の部分がソース配線電極となる。

### 2-2. デバイス性能

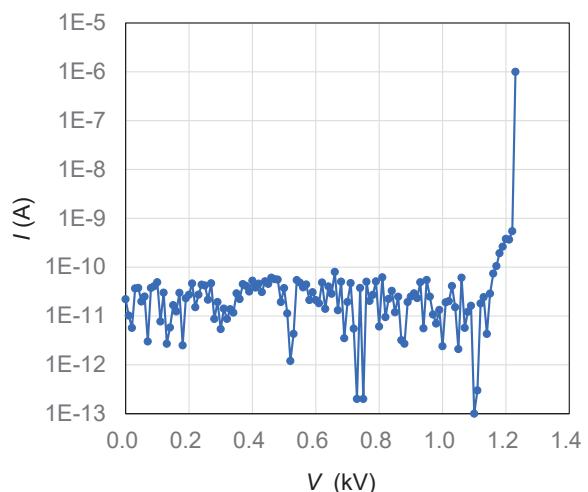

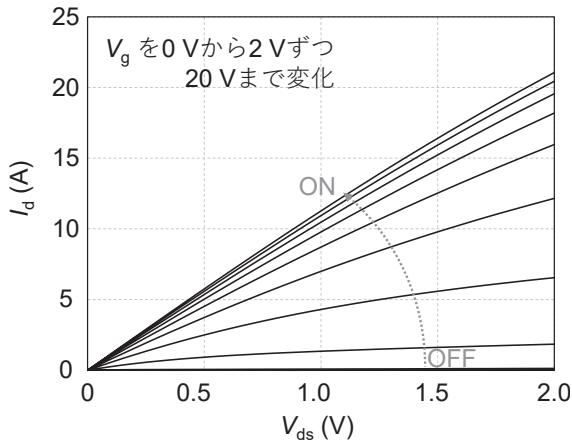

図-3は、縦GaNデバイスと同時に作製した直径200μmのPINダイオードの耐圧特性である。PIN接合のエピ耐圧は1.2kV程度である。縦GaNデバイスの耐圧も、デバイス面積が比較的小さい場合はエピ耐圧と同等の耐圧が得られるが、デバイス面積が大きくなるに従い耐圧は低下する。後述するインバータモジュールの設計は400V駆動であるため、サージ電圧等に対するマージンを考慮して定格を650Vと設定し、この電圧でスクリーニング試験を行い、合格したデバイスをモジュール実装用に選定した。図-4は出力特性であり、定格電流は10～15A程度である。チップ上の4つのデバイスを実装工程で並列接続することで、出力電流は最大4倍まで増すことができるが、プロセス歩留まりの低下が背反となる。これは結晶欠陥やエピゴミなどによるリークの発生頻度が高くなることに起因すると考える。ウエハの更なる高品質化が必要不可欠である。

図-3 φ 200 μm PINダイオードの耐圧特性

図-4 1.5 mm × 1.5 mm サイズ

縦型GaNトレンチMOSFETの出力特性

### 3. インバータ開発

インバータ開発は環境省pjの共同実施者である名古屋大学未来材料・システム研究所トヨタ先端パワーエレクトロニクス寄附研究部門で行われた。以下、概要を述べるが、詳しくは環境省pjの委託業務成果報告書を参照されたい<sup>2)</sup>。

#### 3-1. ハーフブリッジモジュール作製

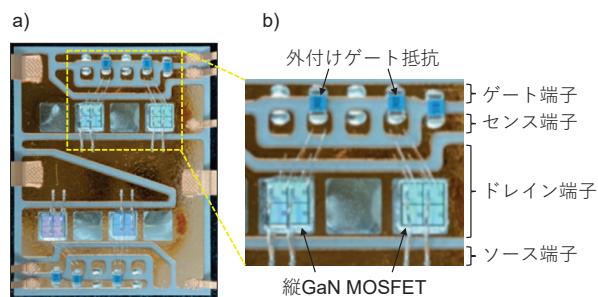

図-5は、もっともシンプルなパワーエレクトロニクス回路の一つであるハーフブリッジモジュールの、樹脂封止前の外観写真である。このモジュールには、放熱設計、配線設計の自由度の高さから、大分デバイステクノロジー株式会社のFLAPモジュールを利用している<sup>15)</sup>。

図-5 ハーフブリッジモジュールの外観写真

(a) 全体像, (b) high サイドの実装部拡大

Highサイド、lowサイドそれぞれに2チップずつ縦GaN MOSFETが実装されている。1チップ上から2つのデバイスをワイヤボンディングで並列接続し、合計4つのデバイスの並列動作で出力電流が40 A級になる設計である。

縦GaN MOSFETに比べて小さいチップは外付けゲート抵抗である。外付けゲート抵抗を付与することでデバイスのスイッチング速度を意図的に遅くし、並列接続したデバイス間の負荷

の偏りが発生しないように調整している。たとえば、並列接続したデバイスの中で比較的動作が速いものにON動作時に電流集中が発生しやすく、そのデバイスだけ発熱が高くなるような故障モードがあるが、そのような負荷集中を防ぐ役割を果たす。

デバイスが実装される銅の多層配線の裏面は、樹脂封止後も露出するようになっており、この部分を水冷ヒートシンクに接触させることでデバイスでの発熱を効率よく放熱することができる。

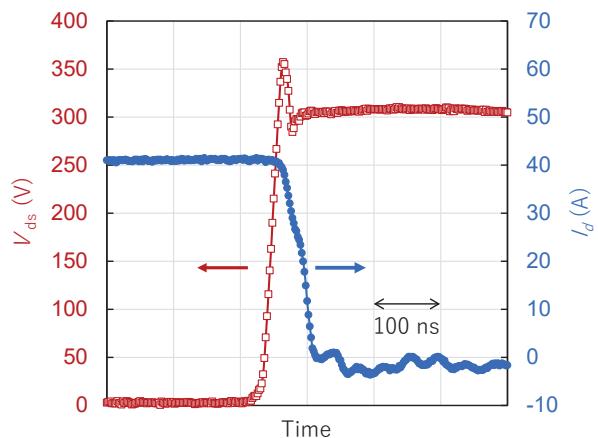

#### 3-2. ハーフブリッジ動作

図-6は、作製したハーフブリッジモジュールのスイッチング動作のターンオフ波形である。ONとOFFの遷移時間は多く見積もって150 ns程度である。デッドタイムを200 ns、ON時間、OFF時間をそれぞれ100 nsと仮定して、およそ1 MHzのスイッチング性能が見込める。モータードライブ用のインバータでは、数十kHzから百数十kHzのスイッチング周波数を用いるので、十分に高速なスイッチングができている。電流、電圧それぞれのリング（スイッチング後の波状のノイズ）も小さい。

図-6 ハーフブリッジモジュールのターンオフ波形

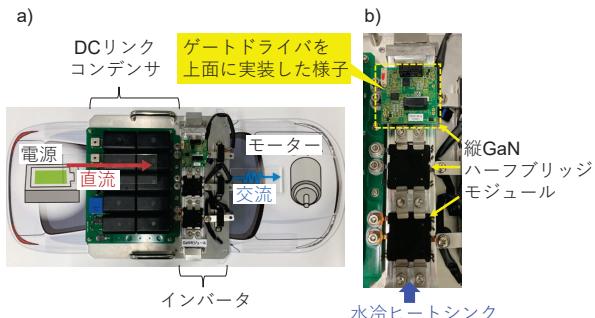

#### 3-3. 三相インバータモジュール

作製したハーフブリッジモジュールを3つ用い、三相のインバータモジュールを構築する。モータードライブ用のインバータは、バッテリーからの直流電力を交流に変換してモーターを駆動させる（図-7）。インバータの前段には、DCリンクコンデンサが配置され電圧レベルを安定化させる。ハーフブリッジモジュールは水冷ヒートシンクに固定され、デバイスからの放熱を促す。ハーフブリッジモジュールの直上にはゲートドライバが搭載され各デバイスの動作を制御する。実際に

電気自動車で使われるインバータの出力は100 kWを超えるが、本開発では出力の目標を10 kWとして、縦GaN MOSFETを使ったインバータ動作の原理検証を行った。

図-7 インバータモジュール

(a) 配置イメージ, (b) インバータ部の拡大写真

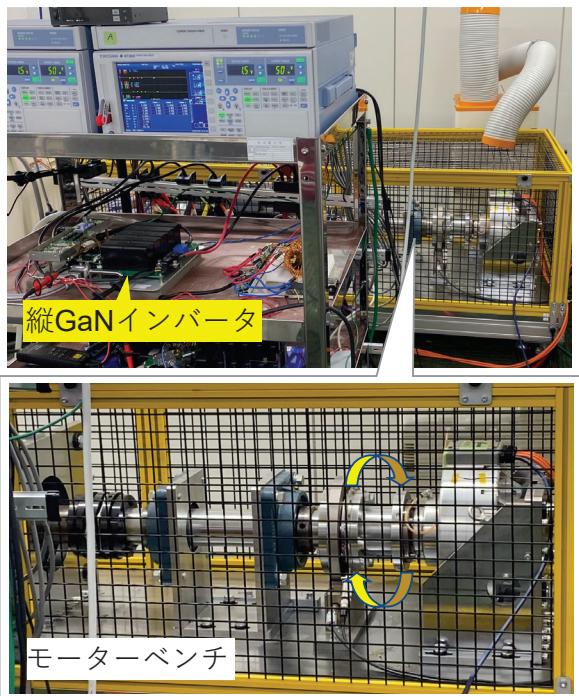

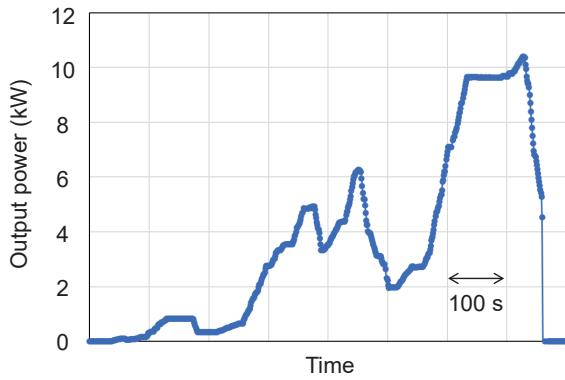

図-8は、構築したインバータモジュールを使ってモーターベンチを駆動させる実験環境である。モーター駆動では徐々に出力を上げ目標の10 kWに到達した(図-9)。出力目標は達成したもの、インバータ動作後のデバイス特性には変動が見られ、この特性変動の低減が今後の課題であり、MOS構造周辺に改善点があると考えられる<sup>13), 14), 16)~21)</sup>。

図-8 モーター駆動実験環境(名古屋大学)

図-9 インバータ出力電力

#### 4.まとめ、今後の展開

縦型GaNトレンチMOSFETと、それを用いたインバータ動作とモーター駆動の実証を行い、目標のインバータ出力10 kWを達成した。インバータ動作実証後のデバイスには特性変動が確認され、主にMOS構造周辺の欠陥などに起因すると考えられる。MOS構造の設計、プロセス技術構築は化合物半導体でのデバイス開発における最難関技術課題の一つと言えるが、GaNパワーデバイス分野の技術発展と市場形成に貢献すべく、この課題解決に邁進する所存である。

#### 謝辞

本研究は環境省「革新的な省CO<sub>2</sub>実現のための部材(GaN)や素材(CNF)の社会実装・普及展開加速化事業」の委託を受けて行われました。

インバータモジュールでのデバイス評価、デバイス信頼性の議論でご協力、ご指導いただいた名古屋大学の塩崎教授、只野教授、成田教授にお礼申し上げます。

#### 参考文献

- 1) 環境省、報道発表資料

<https://www.env.go.jp/press/110692.html>

- 2) 革新的な省CO<sub>2</sub>実現のための部材や素材の社会実装・普及展開加速化事業(超低抵抗GaNウェハを用いた高効率インバータの開発・検証)委託業務成果報告書.令和5年度

- 3) 環境省、GaNパワーデバイスについて

<https://www.env.go.jp/council/06earth/y0618-06/mat04.pdf>

- 4) M. Imanishi et al., *Phys. Status Solidi. RRL*, 18, p. 2400106, (2024).

- 5) M. Kanechika et al., *Jpn. J. Appl. Phys.*, 46, p. L503-L505, (2007).

- 6) D. Shibata et al., *in IEDM Tech. Dig.*, p. 10.1.1-10.1.4, (2016).

- 7) M. Sun et al., *IEEE Electron Device Lett.*, 38, p. 509-512, (2017).

- 8) N. Torii et al., *in IEDM Tech. Dig.*, Dec. (2024).

- 9) H. Otake et al., *Jpn. J. Appl. Phys.*, 46, p. L599-L601, (2007).

- 10) R. Tanaka et al., *Jpn. J. Appl. Phys.*, 59, p. SGGD02, (2020).

- 11) T. Oka et al., *Appl. Phys. Express*, 8, p. 054101, (2015).

- 12) T. Oka et al., Proc. IEEE 31th Int. Symp. Power Semiconductor Devices and ICs, p. 303-306, (2019).

- 13) K. Ito et al., *in IEDM Tech. Dig.*, Dec. (2024).

- 14) T. Kondo et al., *in IEDM Tech. Dig.*, Dec. (2024).

- 15) 大分デバイステクノロジー株式会社, 次世代型パワーモジュール汎用パッケージFLAP

<https://www.odt.co.jp/>

- 16) Y. Irokawa et al., *ECS J. Solid State Sci. Technol.*, 12, p. 055007, (2023).

- 17) M. Fregolent et al., *Microelectron. Reliab.*, 150, p. 115130, (2023).

- 18) Y. Ichikawa et al., *Jpn. J. Appl. Phys.*, 63, p. 02SP31, (2024).

- 19) N. Zagni et al., *J. Semicond.*, 45, p. 032501, (2024).

- 20) M. Henn et al., *IEEE Trans. Electron Devices*, 71, p. 1553-1560, (2024).

- 21) J. Nishii et al., *Microelectron. Reliab.*, 投稿準備中

## 著 者

西井潤弥

長谷川一也

田中成明

丹羽隆樹